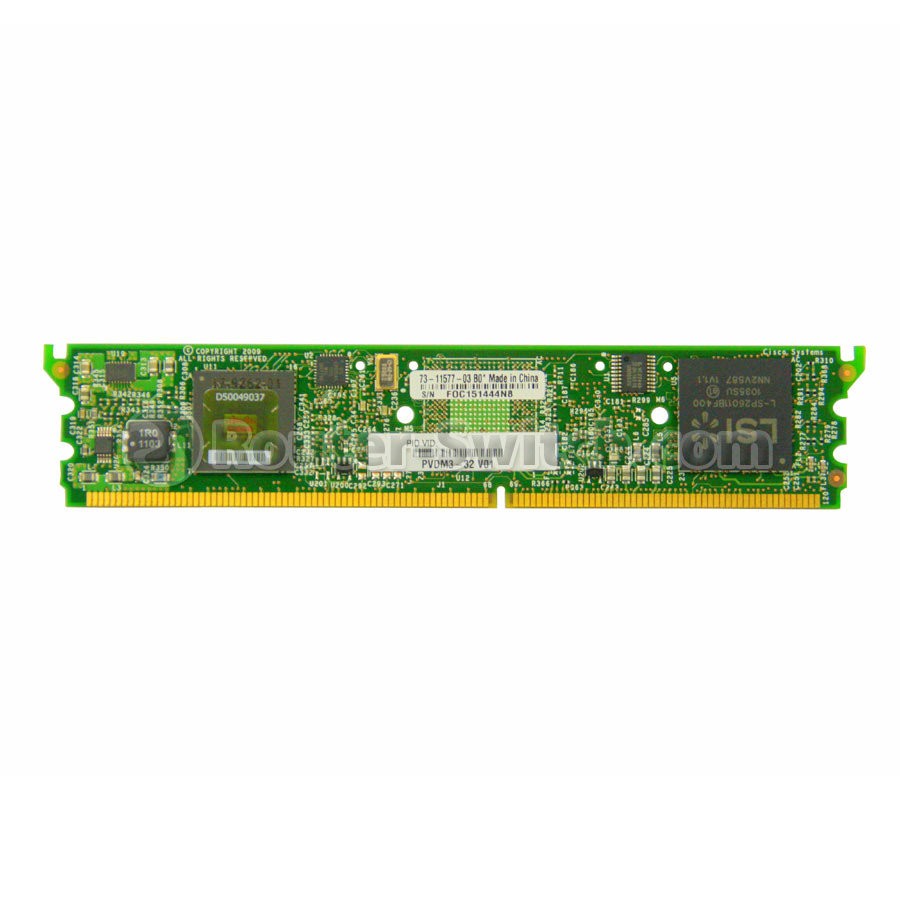

PVDM3-128 Specification

PVDM3 Modules Specifications |

|

|

Components |

|

|

DSP |

Multicore DSP technology |

|

DSP external memory |

512-megabit double-data-rate (DDR) synchronous dynamic random access memory (SDRAM) for each DSP |

|

Interface |

240-pin dual-inline-memory-module (DIMM) interface |

|

Features |

|

|

Echo cancellation |

Software echo cancellation compliant with ITU-T G.168, with 128-ms tail coverage |

|

Operating temperature |

-41 to 131 ?F (-5 to 55 ?C) |

|

Voltage |

3.3V |

|

Current |

1.47A |

|

Power |

4.85W |

|

Regulatory and Compliance |

|

|

Safety |

?? Complies with IEC 60950 (worldwide) and AS/NZS 60950-1 (Australia and New Zealand), CAN/CSA-C22.2 No. 60950-1, 1st and 2nd Ed. (Canada), and GB4943-95 (People’s Republic of China) ?? EN60950-1, 1st and 2nd Ed. (CENELEC; includes EU and EFTA) ?? NOM-019-SCFI-1998 (Mexico), and UL 60950-1, 1st and 2nd Ed. (United States) |

|

Homologation |

Platform dependent |

|

Mean time between failure (MTBF) |

System dependent |

|

EMC |

|

|

Emissions |

?? CISPR22, Class B ?? EN55022, Class B, CFR47, Part 15, Subpart B, Class B |

|

Harmonics |

EN61000-3-2 |

|

Flicker |

EN61000-3-3 |

|

Immunity |

?? CISPR24 ?? EN 55024 ?? EN50082-1 |

|

Electrostatic discharge (ESD) |

EN 61000-4-2 |

|

RF fields |

EN 61000-4-3 |

|

EFT |

EN 61000-4-4 |

|

Surge |

EN 61000-4-5 |

|

Conducted RF |

EN 61000-4-6 |

|

Power-frequency magnetic fields |

EN 6100-4-8 |

|

Voltage dips, sags, and interruptions |

EN 61000-4-11 |